[전기전자 기초 #23] 클럭 신호(Clock Signal)와 클럭 분배(Clock Distribution) | 디지털 회로의 심장

안녕하세요 😊

오늘 배울 내용은 클럭 신호 와 동기화 입니다.

디지털 회로 의 정확한 시간 동작을 유지하기 위해 클럭 신호(Clock Signal)가 필요합니다.

클럭 신호는 0과 1의 주기적인 반복을 통해 모든 회로의 동작을 동기화(Synchronization)합니다.

그럼 바로 클럭 신호(Clock Signal) 와 동기화(Synchronization) 에 대해 알아보겠습니다.

✅ 클럭 신호(Clock Signal)란?

클럭 신호(Clock Signal)는 디지털 회로에서 동작의 타이밍을 맞추기 위한 주기적인 신호입니다.

0과 1이 일정한 주기로 반복되며, 모든 동기식 회로의 동작을 동기화(Synchronization) 시킵니다.

💡 비유:

클럭 신호는 마치 기차 시간표와 같습니다.

기차가 정해진 시간에 도착하고 출발하듯, 디지털 회로도 클럭 신호에 맞춰 동작합니다.

🔌 클럭 신호의 주요 특징

| 특징 | 설명 |

| 주기적 반복 | 0 → 1 → 0 → 1 … 반복 |

| 정확한 시간 제어 | 모든 회로가 같은 시간에 동작 |

| 주파수(Frequency) | 초당 반복 횟수 (Hz) |

| 펄스 폭(Pulse Width) | 1 사이클 내의 High 또는 Low 상태 시간 |

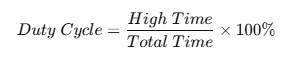

| 듀티 사이클(Duty Cycle) | High 상태의 비율 (%) |

✔️ 클럭 신호의 파형

- 주기 (T): 한 사이클이 반복되는 시간

- 주파수 (f): 1초당 사이클 반복 횟수

- 듀티 사이클: High 상태의 비율

🎨 클럭 신호의 예시

아래와 같은 파형이 발생합니다.

- 50% 듀티 사이클

_____ _____

| | | |

| | | |

|_____|___|_____|___- 25% 듀티 사이클

___ ___

| | | |

| | | |

|___|_____|___|_____🔄 클럭 분배(Clock Distribution)란?

클럭 분배(Clock Distribution)는 생성된 클럭 신호를 시스템 전체에 전달하는 과정입니다.

클럭 신호가 모든 회로에 동시에 전달되어야 정확한 타이밍을 유지할 수 있습니다.

💡 비유:

클럭 분배는 마치 전력 공급망과 같습니다.

발전소에서 만들어진 전기가 각 가정에 고르게 전달되듯,

클럭 신호도 모든 회로에 정확하게 전달되어야 합니다.

🔄 클럭 분배(Clock Distribution)

- 생성된 클럭 신호를 시스템 전체에 고르게 전달합니다.

- 트리 구조, H-Tree 구조, 메쉬 구조 등이 있으며,

고성능 시스템에서는 H-Tree 구조를 많이 사용합니다.

✔️ 클럭 분배 방식

| 방식 | 설명 | 장점 | 단점 |

| 트리 구조 (Tree Topology) | 클럭 소스에서 분기하여 전달 | 간단한 설계 | 지연 시간 발생 |

| H-Tree 구조 | 균일한 지연을 위해 대칭 구조 | 동기화가 쉽다 | 배선 복잡 |

| 메쉬 구조 (Mesh Topology) | 여러 경로로 클럭 전달 | 신뢰성 높음 | 면적 차지 |

🎨 클럭 분배 예시

1️⃣ 트리 구조

CLK

|

+---+---+

| |

CLK1 CLK22️⃣ H-Tree 구조

+-----+

| CLK |

+--+--+

|

+-----+-----+

| |

CLK1 CLK2✔️ 클럭 신호의 문제점과 해결책

| 문제점 | 설명 | 해결책 |

| 클럭 지연 (Clock Skew) | 전달 경로에 따른 시간 차이 | 버퍼 삽입, 최적화 |

| 클럭 지터 (Clock Jitter) | 주기가 불규칙하게 흔들림 | 고정된 주파수 발생기 사용 |

| 클럭 드리프트 (Clock Drift) | 온도 변화로 인한 주파수 변동 | PLL (Phase-Locked Loop) 사용 |

💡 실무 팁:

고성능 CPU나 메모리 시스템에서는 H-Tree 구조를 많이 사용합니다.

이유는 모든 노드에 같은 시간에 신호가 전달되기 때문입니다.

⚡ 실무에서 클럭 신호와 클럭 분배 활용 예시

| 용도 | 타이밍 |

| 🖥️ CPU 타이밍 제어 | 명령어 처리 순서 동기화 |

| 📡 네트워크 라우팅 | 데이터 패킷 전송 시간 조정 |

| 🏠 스마트 홈 시스템 | 센서와 디바이스 동기화 |

| 🎮 게임 컨트롤러 | 입력 신호 처리 간격 조절 |

🧠 오늘의 요약

- 클럭 신호(Clock Signal)는 디지털 회로의 시간 동작을 제어하는 기본 신호입니다.

- 주기, 주파수, 듀티 사이클 개념이 있으며, 일정한 반복으로 회로를 동기화합니다.

- 클럭 분배(Clock Distribution)는 클럭 신호를 모든 회로에 정확하게 전달합니다.

- CPU, 메모리, 통신 네트워크 등에서 시간 동기화를 필수적으로 사용합니다.

정확한 클럭 신호와 효율적인 클럭 분배는 CPU, 메모리, 네트워크 시스템의 정확한 동작을 보장합니다.

📌 다음 글 예고

다음 시간에는 플립플롭에 대한 심화적인 내용에 대하여 알아보겠습니다.

읽어주셔서 감사합니다 😊

유익했다면 댓글과 공감 부탁드려요!